SRAM到底是什么?它为何在芯片界仍不可替代?

静态随机存取存储器(SRAM)利用触发器保存数据,不需要周期性刷新,因此**读写延迟极低、功耗可预测**。在CPU缓存、网络处理器、FPGA、汽车ECU等场景中,SRAM仍是**速度与可靠性**的代名词。

2024—2028年全球SRAM市场走向

需求端:三大增量引擎

- AI推理芯片:边缘端推理模型参数规模暴涨,L2/L3缓存容量从16 MB迈向128 MB,推动**高密度SRAM**订单。

- 车载域控制器:L3以上自动驾驶要求功能安全等级ASIL-D,**车规级SRAM**(-40℃~150℃)需求年复合增速达18%。

- 5G小基站:O-RU需要极低延迟的包缓冲,**同步SRAM(Sync SRAM)**成为BBU与RU之间的数据桥梁。

供给端:工艺演进与产能瓶颈

目前6T SRAM单元已逼近**物理极限**,三星、台积电、英特尔在3 nm节点引入**GAA晶体管**与**Vts微调**技术,将单元面积缩小至0.021 µm²,但良率仅60%。与此同时,**成熟制程(28/22 nm)**产能被车规、工业芯片长期锁定,导致**中低密度SRAM**交期仍长达26~30周。

---如何挑选最适合项目的SRAM芯片?

第一步:先锁定容量与位宽

自问:我的系统需要多大的数据暂存?

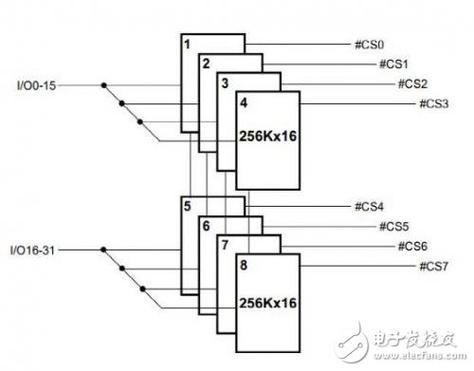

答:以FPGA图像处理为例,1080p@60 fps帧缓存约需8 MB,若采用**32-bit位宽**的8 M×32器件,只需一颗即可;若用16-bit位宽则需两颗并联,布线复杂度翻倍。

第二步:速度等级怎么选?

- CPU L2缓存:≤2 ns访问延迟,选**QDR-IV 1066 MHz**。

- 车载网关:对延迟容忍度高,可选**10 ns异步SRAM**,成本下降35%。

第三步:功耗与数据保持电流

低功耗IoT节点需关注**ISB2**(待机电流)。例如Cypress的65 nm工艺8 Mbit器件,ISB2仅6 µA,而90 nm旧工艺高达25 µA,**电池寿命可延长4倍**。

第四步:封装与可靠性认证

| 场景 | 推荐封装 | 认证标准 |

|---|---|---|

| 工业控制 | TSOP-44 | AEC-Q100 Grade 2 |

| 航空航天 | Ceramic CQFP-100 | MIL-PRF-38535 |

| 便携医疗 | WLCSP-36 | IEC 60601-1 |

价格与交期:2024年Q2最新情报

根据TechInsights与Supplyframe联合数据:

- 4 Mbit异步SRAM:单价0.45 USD,交期20周。

- 72 Mbit QDR-II+:单价12.8 USD,交期32周,**仅Cypress、Renesas两家有货**。

- 车规级16 Mbit:单价2.1 USD,**溢价25%**,但Tier-1厂商仍排队锁单。

未来五年,哪些技术可能颠覆传统SRAM?

1. eMRAM与FeRAM缓存替代

虽然eMRAM写入速度已缩短至3 ns,但**读延迟仍比SRAM高一个数量级**,短期内仅用于L4缓存或存储级内存。

2. 3D SRAM(3DS)堆栈

台积电SoIC技术可把8层SRAM die堆叠到CPU上方,**带宽提升5倍**,散热功耗墙成为最大挑战。

3. 存内计算(PIM-SRAM)

通过在6T单元旁嵌入**模拟乘法器**,实现向量乘加就地完成,**能效提升20倍**,但精度目前仅限INT8。

---实战案例:用Excel快速做SRAM选型决策

- 在A列列出容量、B列速度、C列功耗、D列单价、E列交期。

- 用公式=B2*0.4+C2*0.3+D2*0.2+E2*0.1生成加权得分。

- 得分最低的三颗料号进入原理图验证阶段,**两周内即可锁定BOM**。

常见疑问快答

Q:SRAM与DRAM混用会不会有兼容性问题?

A:只要控制器支持**不同协议时序**,并在PCB上用Fly-by拓扑隔离时钟线,即可混用。

Q:国产SRAM可靠性如何?

A:北京君正、武汉新芯已推出40 nm车规级样品,**HTOL 1000 h失效率<10 ppm**,与瑞萨差距缩小到一代工艺。

评论列表