一、电子连接器选型技巧:从需求到落地的全流程拆解

很多工程师在拿到原理图后,第一反应是“找现货”,结果常常出现插拔力过大、温升超标、EMI不过等问题。选型其实有一套可复制的逻辑:

- 先锁定电气指标:额定电流、耐压、接触电阻是硬门槛,直接决定能否通过安规。

- 再核对机械维度:板到板高度、锁扣方式、防呆键位必须与结构工程师反复确认。

- 最后评估供应链:交期、MOQ、替代料号、生命周期,缺一不可。

二、高速连接器如何降低信号损耗:5个实测有效的工程手段

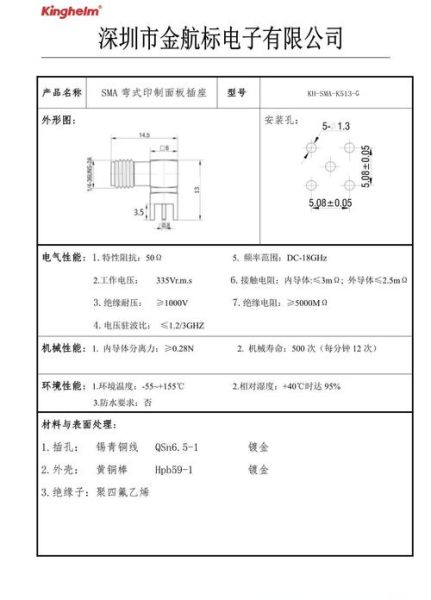

10Gbps以上速率时,连接器不再是“金属+塑料”的简单组合,而是传输线的一部分。以下方法已在PCIe Gen4/5、56G-PAM4背板中验证:

1. 阻抗连续性设计:把“台阶”削平

问:为什么仿真曲线在1.5 GHz处出现尖峰?

答:多半是接触区与PCB焊盘之间的阻抗突变。解决思路:

- 缩短引脚 stub,优先选press-fit或表面贴封装;

- 在焊盘下方加背钻(back-drill),把多余过孔铜柱掏掉;

- 用三维场求解器微调焊盘 anti-pad 直径,±2 mil 就能拉回5 Ω。

2. 材料升级:从黄铜到铍铜再到铜合金镀层

传统黄铜导电率只有26% IACS,而高性能铜合金C7025可达50% IACS,且保持同等弹性模量。镀层顺序也有讲究:

- 打底1.3 μm镍,防扩散;

- 中间0.2 μm钯镍,抗腐蚀;

- 最外层0.05 μm硬金,保证插拔寿命。

3. 屏蔽与接地:让回流路径贴着信号走

高速差分对最怕共模噪声。实测发现,在连接器两侧加360°金属屏蔽弹片,可把近端串扰降低8 dB。关键细节:

- 弹片与机壳地之间多点接地,间距≤λ/20;

- 内部差分对之间加接地针(ground pin),形成“篱笆”效应。

4. 插入损耗预算:系统级思维

问:连接器损耗到底该留多少 dB?

答:按信道总预算-PCB-IC封装=连接器余量反推。举例:

| 项目 | PCIe Gen4 16 GT/s |

|---|---|

| 信道总预算 | -28 dB@8 GHz |

| PCB走线 | -18 dB |

| IC封装 | -4 dB |

| 留给连接器 | -6 dB |

如果实测连接器-7.5 dB,就必须缩短走线或换更低损耗板材。

5. 测试验证:眼图不是唯一标准

除了眼图,还要跑:

- COM(Channel Operating Margin):把抖动、噪声、码间干扰全部量化;

- TDR阻抗扫描:定位±10%阻抗偏差的精确位置;

- 多温度循环:-40 ℃~85 ℃重复插拔500次,看接触电阻漂移。

三、实战案例:56G-PAM4背板连接器的降损之路

某通信客户在28层背板上跑56G-PAM4,初期眼图闭合。排查步骤:

- 发现连接器引脚 stub 长达1.8 mm,导致-15 dB插入损耗;

- 换成press-fit短stub版本,损耗降至-10 dB;

- 在连接器下方加背钻,再降2 dB;

- 最终通过预加重+CTLE均衡,眼图裕量>0.25 UI。

四、未来趋势:224G-PAM4对连接器的极限挑战

当单通道速率迈向224 Gbps,连接器必须解决:

- 介电损耗:传统LCP介电常数3.7,需改用改性PPS或PTFE;

- 表面粗糙度:铜箔Rz从2 μm降到0.5 μm,可减少0.3 dB/inch损耗;

- 共封装光学(CPO):把光引擎直接做在交换芯片旁,彻底绕过铜互连瓶颈。

五、常见疑问快答

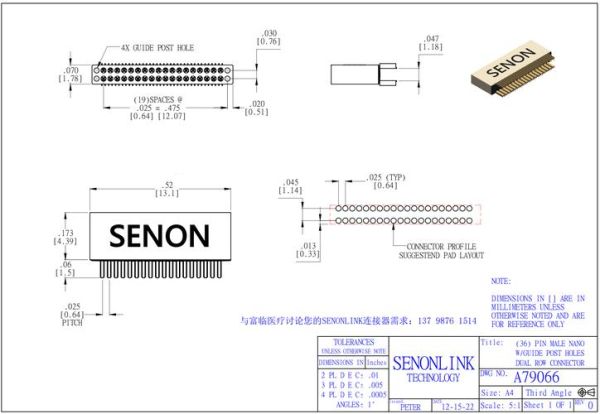

Q:板到板连接器选0.8 mm pitch还是0.5 mm pitch?

A:0.5 mm pitch密度高,但载流能力下降到0.3 A/pin,且加工成本高20%。除非空间极限,否则优先0.8 mm。

Q:高速连接器可以二次回流焊吗?

A:看塑壳材质。LCP可耐260 ℃×3次,PPS只能260 ℃×1次。二次回流前务必做X-ray空洞率检测。

Q:镀层厚度越厚越好?

A:金厚>0.8 μm反而让插拔力增大,且成本指数级上升。0.05 μm硬金+0.2 μm钯镍是性价比最优解。

评论列表